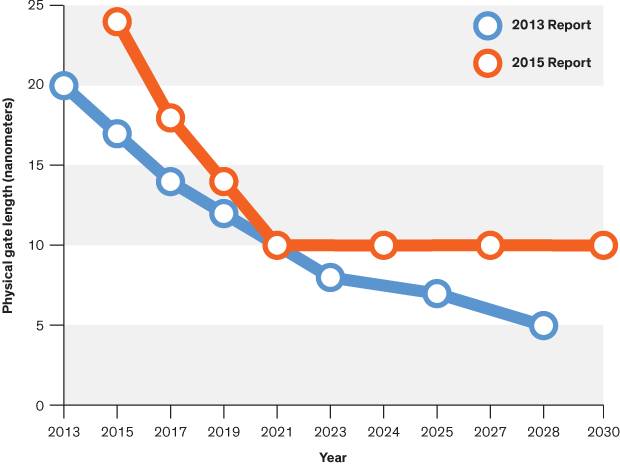

After 2021, the report forecasts, it will no longer be economically desirable for companies to continue to shrink the dimensions of transistors in microprocessors. Instead, chip manufacturers will turn to other means of boosting density.

In fact this is the last ITRS roadmap and the end to a more-than-20-year-old coordinated planning effort that began in the United States and was then expanded to include the rest of the world.

However the Semiconductor Industry Association, which represents IBM and Intel said that people are just not interested any more and it will have to do its own work, in collaboration with another industry group, the Semiconductor Research Corporation, to identify research priorities for government. Other ITRS participants will continue on with a new roadmapping effort under a new name, which will be conducted as part of an IEEE initiative called Rebooting Computing.

Analysts say that the difficulty and expense associated with maintaining Moore’s Law research has since resulted in significant consolidation. In 2001 there were 19 companies that were developing and manufacturing logic chips with leading-edge transistors. Now there is just Intel, TSMC, Samsung, and GlobalFoundries.

They can communicate directly to their equipment and materials suppliers and don't want to sit down and tell their rivals what they are up to.

Semiconductor companies that no longer make leading-edge chips in house rely on the foundries that make their chips to provide advanced technologies. What’s more, he says, chip buyers and designers are increasingly dictating the requirements for future chip generations.

This final ITRS report is titled ITRS 2.0. The name reflects the idea that improvements in computing are no longer driven from the bottom up, by tinier switches and denser or faster memories. Instead, it takes a more top-down approach, focusing on the applications that now drive chip design, such as data centers, the Internet of Things, and mobile gadgets.

The new IEEE roadmap—the International Roadmap for Devices and Systems—will also take this approach, but it will add computer architecture to the mix, allowing for “a comprehensive, end-to-end view of the computing ecosystem, including devices, components, systems, architecture, and software,” according to a recent press release.

Transistor miniaturization was still a part of the long-term forecast as recently as 2014, when the lastITRS report was released. That report predicted that the physical gate length of transistors—an indicator of how far current must travel in the device—and other key logic chip dimensions would continue to shrink until at least 2028. But 3D concepts have gained momentum. The memory industry has already turned to 3D architectures to ease miniaturisation pressure and boost the capacity of NAND Flash. Monolithic 3D integration, which would build layers of devices one on top of another, connecting them with a dense forest of wires.

Moore’s Law just predicted how many transistors can fit in a given area of IC. Company still could make transistors smaller well into the 2020s, but it’s more economic to go 3-D.

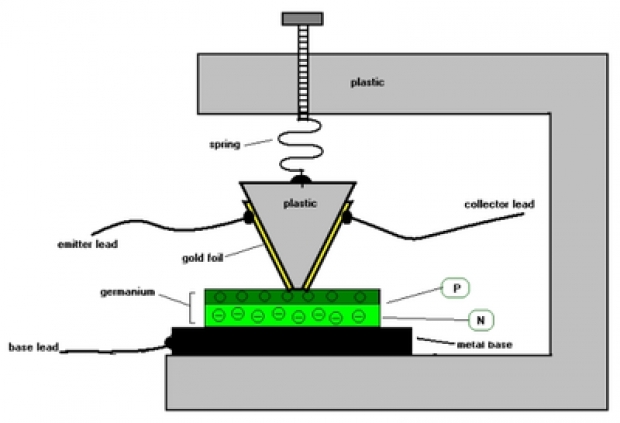

Before 3-D integration is adopted, the ITRS predicts that leading-edge chip companies will move away from the FinFET transistor structure. According to the roadmap, chipmakers will leave that in favor of a lateral, gate-all-around device that has a horizontal channel like the FinFET but is surrounded by a gate that extends underneath. After that, transistors will become vertical, with their channels taking the form of pillars or nanowires. The traditional silicon channel will also be replaced by channels made with alternate materials, namely silicon germanium, germanium, and compounds drawn from columns III and V of the periodic table.

The doubling of transistor densities hasn’t been linked to improvements in computing performance for ages anyway. In the good old days shrinking transistors meant faster speeds, but by the 90s the extra metal layers that were added to wire up increasing numbers of transistors were adding significant delays and performance was improved by redesigned chip microarchitectures. In 2000 the main issue was heat because transistor densities were so high that their heat limited clock speeds. Companies began packing multiple cores on chips to keep things moving.