Sonoma is supposed to be a "low-cost SPARC processor for enterprise workloads." The chip uses the SPARC M7 design, DDR4 memory interfaces, PCIe electronics and InfiniBand interfaces in a single package. Eight SPARC 4th generation cores, hooks into the system RAM and built using a 20nm process with 13 metal layers.

Each package has a shared 8MB L3 cache, shared L2 caches with 512KB per core pair and private L1 32KB caches.

There are two DDR4 memory controllers, each with four DDR4-2133/2400 channels, up to two DIMMs per channel, and up to 1TB of DRAM per socket. Oracle it can manage 77GB/s bandwidth with the wind behind it and if it is going downhill.

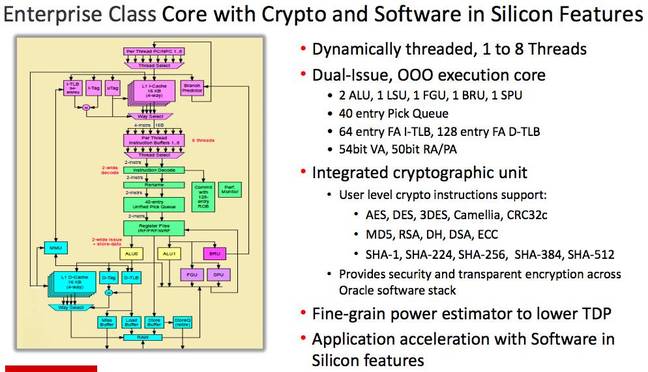

Basant Vinaik, Oracle's senior principal engineer of CPU and I/O verification, told the Hot Chips conference that Sonoma contains a crypto-unit with user-level crypto instructions.

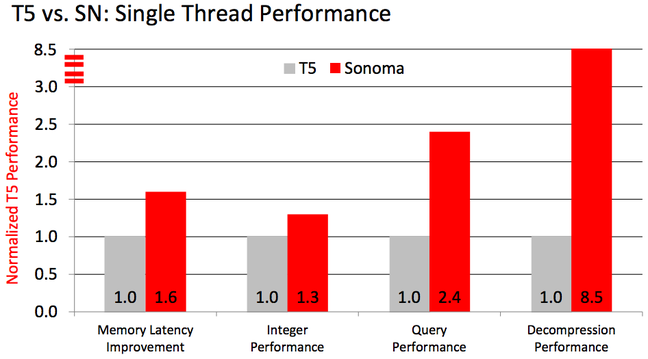

"The cache has been optimized to reduce latency and increase throughput. Sonoma achieves low latency with its integrated memory controller. We use speculative memory read to do this. Software can tune this using threshold registers."