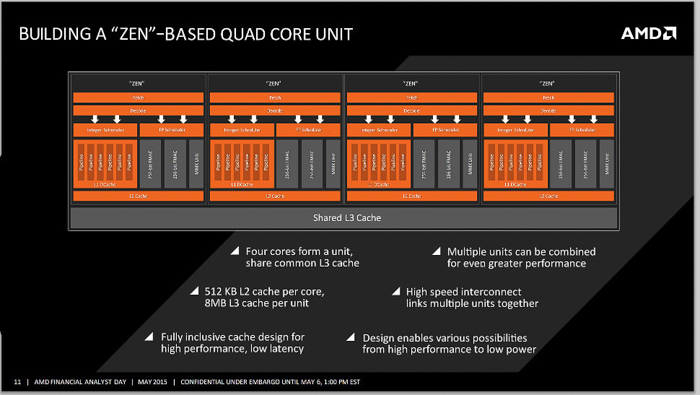

AMD's Zen-based quad-core unit slide from May 6, 2015. (Larger image here)

AMD’s official “Zen-based Quad Core Unit” slide” was released May 6, 2015 during its Financial Analyst Day when the company claimed its new platform will have a more competitively-focused IPC design, higher core counts, lower latency caches and will be based on second-generation 14nm Low-Power Plus (LPP) process technology.

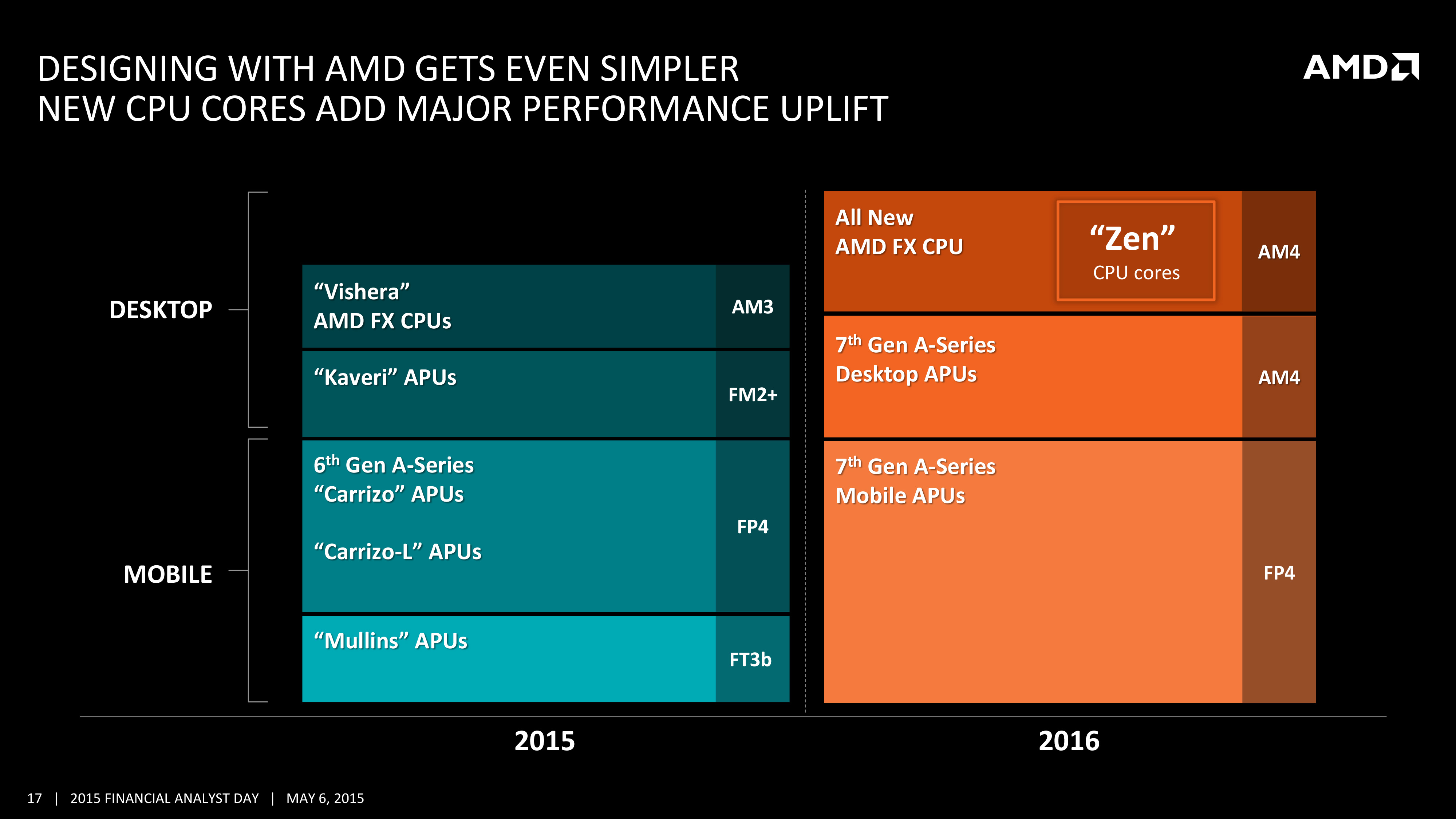

AMD's Zen FX CPU roadmap slide from May 6, 2015. (Larger image here)

On Wednesday, sources close to the folks at Italian site Bitsandchips.it now suggest that AMD will produce 8-core and 6-core Zen x86 chips initially – and only in the event of bad yields will OEMs and ODMs decide to use quad-core variants. Due to the fact that Intel is launching 6-core and 10-core high-end Broadwell-E processors later this month, it appears AMD will be initially focused on bringing back some high-end desktop (HEDT) market share from Intel’s stagnant performance numbers.

In recent benchmarks, the Core i7 6950X is only about 10 percent faster than the Core i7 5960X in Cinebench multi-threaded performance, while the former Haswell-E chip is actually slightly faster in Cinebench single-threaded tests. This is a great place for AMD to gain some ground against Intel’s ‘Kaby Lake’ CPUs in Instructions Per Clock (IPC) by launching Zen with a higher number of cores, at least initially.

We mentioned in August 2015 that Zen uses SMT (hyperthreading) just like Intel’s cores and will be switching back to a single FPU-per core design. With this market approach, every core will be able to run two simultaneous threads just like Intel’s CPUs. This is AMD’s way of breaking from the “core pair” implementation that was established in Bulldozer in October 2011, also known as Clustered Multithreading (CMT).

Of course, AMD will eventually release a 16-core x86 Zen APU with Greenland integrated graphics, but this is not expected to compete with Intel until 2017 when 10-nanometer Cannonlake CPUs are released later in the year. AMD can also produce an 8-core and even 6-core version of this Zen APU.

Bristol Ridge APUs will initially take dual-core and quad-core designs

Meanwhile, the company is planning to announce some new dual-core and quad-core APUs later this month at Computex 2016, codenamed Bristol Ridge, to compete with current Intel 6th-generation Skylake CPUs. These 7th-generation APUs are built using four ‘Bulldozer’ CPU cores and eight GPU cores, and AMD will categorize them as “entry level” CPUs when they launch later this summer. Already, HP has announced an Envy x360 15-inch convertible with dual-core and quad-core Bristol Ridge parts based on the AMD FX naming scheme.

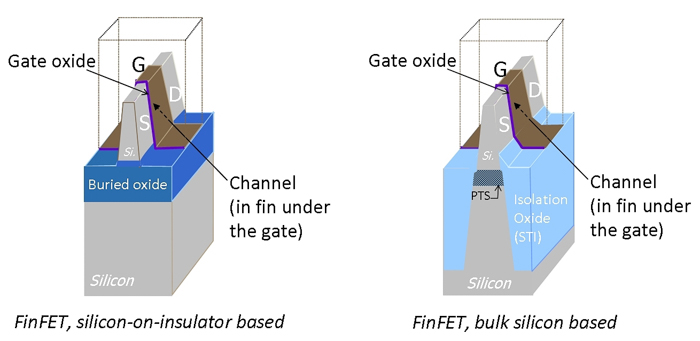

GlobalFoundries has been ramping up production of its second-generation 14-nanometer technology, also known as 14 Low-Power Plus (14LPP) since Q4 2014 and provided some validation on production samples in December 2015. AMD has said in the past that it will not pay GlobalFoundries (or any foundry) to develop custom silicon for its architectural designs. With this in mind, the company is relying heavily on the success of the GF second-gen 14LPP process technology and fully-depleted silicon technology to restore its core PC business back to levels it has not experienced in years. The improvements should help AMD gain traction in both TDP efficiency and performance that will allow the company to effectively scale Zen designs across more market segments in years to come.

Fully depleted FinFET transistors (one fin shown here) — silicon-on-insulator vs. bulk silicon