AMD is fast tracking stacked DRAM deployment and a new presentation leaked by the company points to APUs with stacked DRAM, or high bandwidth memory (HBM).

AMD is calling the project "Fastforward" and it is all about boosting memory bandwidth on upcoming APUs. However, AMD is not talking about specific products yet and it is unclear whether HBM will be implemented on its upcoming Carizzo APU. This seems highly unlikely at this point for a number of reasons and if we were to speculate we would say HBM is coming to the next-next generation of AMD APUs.

Stacked DRAM APUs to deliver up to 128GBps bandwidth

Using two DRAM stacks AMD could boost bandwidth at an unprecedented rate. Two stacks would result in a 1024-bit interface and up to 128GBps bandwidth. GDDR5 maxes out at 32 bits and 28GBps. With one stack in play the results are somewhat lower, 512-bit bus and 64GBps bandwidth.

AMD says it is looking at 1.2V+ DRAM with 2Gb per stack and 4 DRAM modules per stack. However, the presentation states that AMD is currently conducting evaluations of "various architectures and interface options," so it could be a while before we see what exactly it has in mind.

AMD's Fastforward objectives

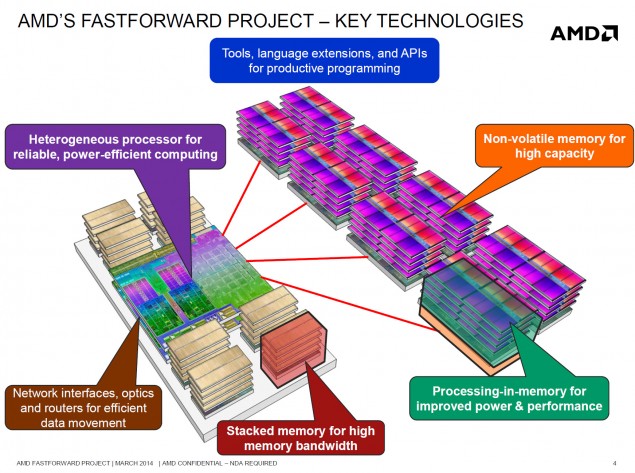

Stacked DRAM is just part of the story, as AMD's Fastforward initiative is a bit broader. The company says its principle Fastforward objective is to investigate processor and memory technologies for exascale systems based on high volume architectures and open standards.

The end result should "provide significant benefits" to high volume markets and the chipmaker says it is "based on extending high volume APU architecture."

The list of key technologies which are part of the fastforward project is quite long. HSA, stacked DRAM, new APIs, non-volatile memory and processing-in-memory are just some of them.

The presentation was leaked on 3DCenter forums and the pdf can be found here.